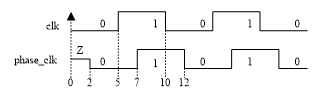

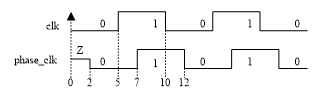

根据下面的程序,画出产生的信号clk、phase_clk的波形如图所示`timescale 1ns/10ps module clk_tb2; reg clk; wire phase_clk; initialclk=0; always begin #5 clk=1; #5 clk=0; endassign #2 phase_clk=clk endmodule ( )

( )

( )

( )举一反三

- 根据下面的程序,画出产生的信号clk、phase_clk的波形如图所示`timescale 1ns/10ps module clk_tb2; reg clk; wire phase_clk; initialclk=0; always begin #5 clk=1; #5 clk=0; endassign #2 phase_clk=clk endmodule[img=314x94]17d603ead880b55.png[/img] ( )

- (多选题, 2分)时钟上升沿检测语句可以是? A: CLK'EVENT AND CLK='1' B: CLK'EVENT AND CLK='0' AND CLK'LAST_VALUE='1' C: CLK'LAST_VALUE='1' AND CLK='0' D: RISING_EDGE(CLK) E: FALLING_EDGE(CLK) F: CLK'EVENT AND CLK='1' AND CLK'LAST_VALUE='0' G: CLK'LAST_VALUE='0' AND CLK='1'

- 时钟信号CLK在进程中为敏感信号,可用于检测CLK上升沿的语句有 A: IF CLK'EVENT AND CLK=‘1’ B: IF CLK'EVENT AND CLK=‘0’ C: IF CLK=‘1’AND CLK'LAST_VALUE =‘0’ D: IF rising_edge(CLK) E: IF CLK=‘1’ F: wait until CLK=‘1’

- always begin # 5 clk=0;# 20 clk=~clk ;end 产生的波形下列说法正确的是( )。 A: 周期为 20 B: 空比为1/4 C: 占空比为1/5 D: clk=1

- module CNT4(CLK,Q); output [3:0] Q; input CLK;reg ____ Q1 ; always @(posedge CLK)Q1 = Q1+1 ;assign Q = Q1; endmodule空格处应该填入: A: reg B: CLK C: Q1 D: [3:0]